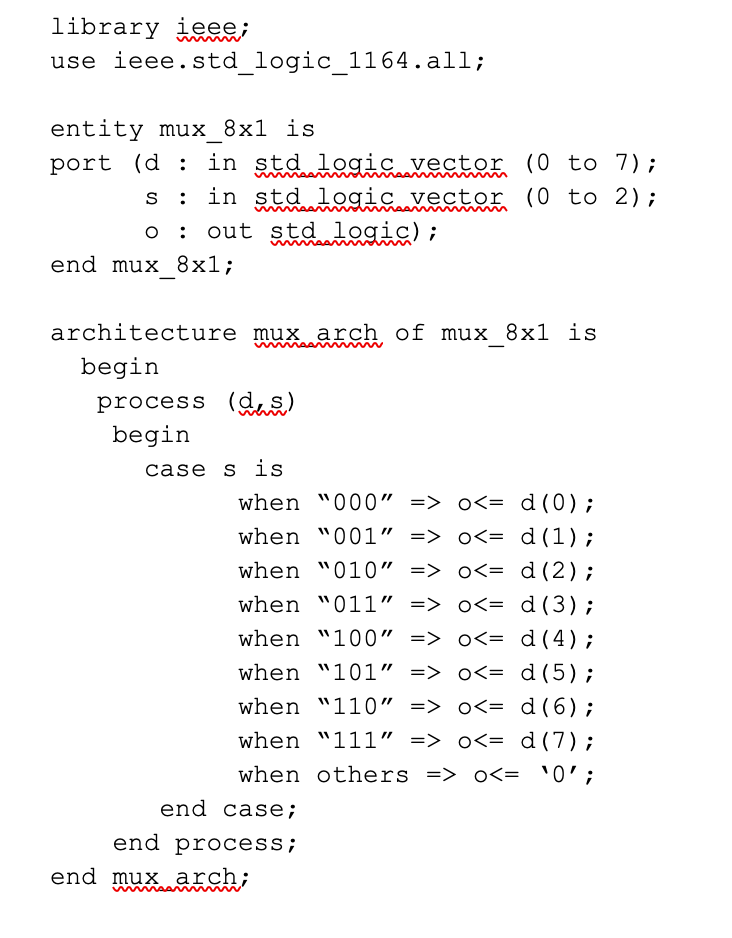

23+ pages vhdl code for 8 to 1 multiplexer using if statement 725kb solution in Doc format . Entity multiplexer8_1 is port din. In behavioral modeling we have to define the data-type of signalsvariables. Using the Boolean expression that describes a 4-to-1 MUX in the previous section. Check also: vhdl and vhdl code for 8 to 1 multiplexer using if statement Connect the first 8 to each of the 64 inputs then connect the ninth to the outputs of the first eight.

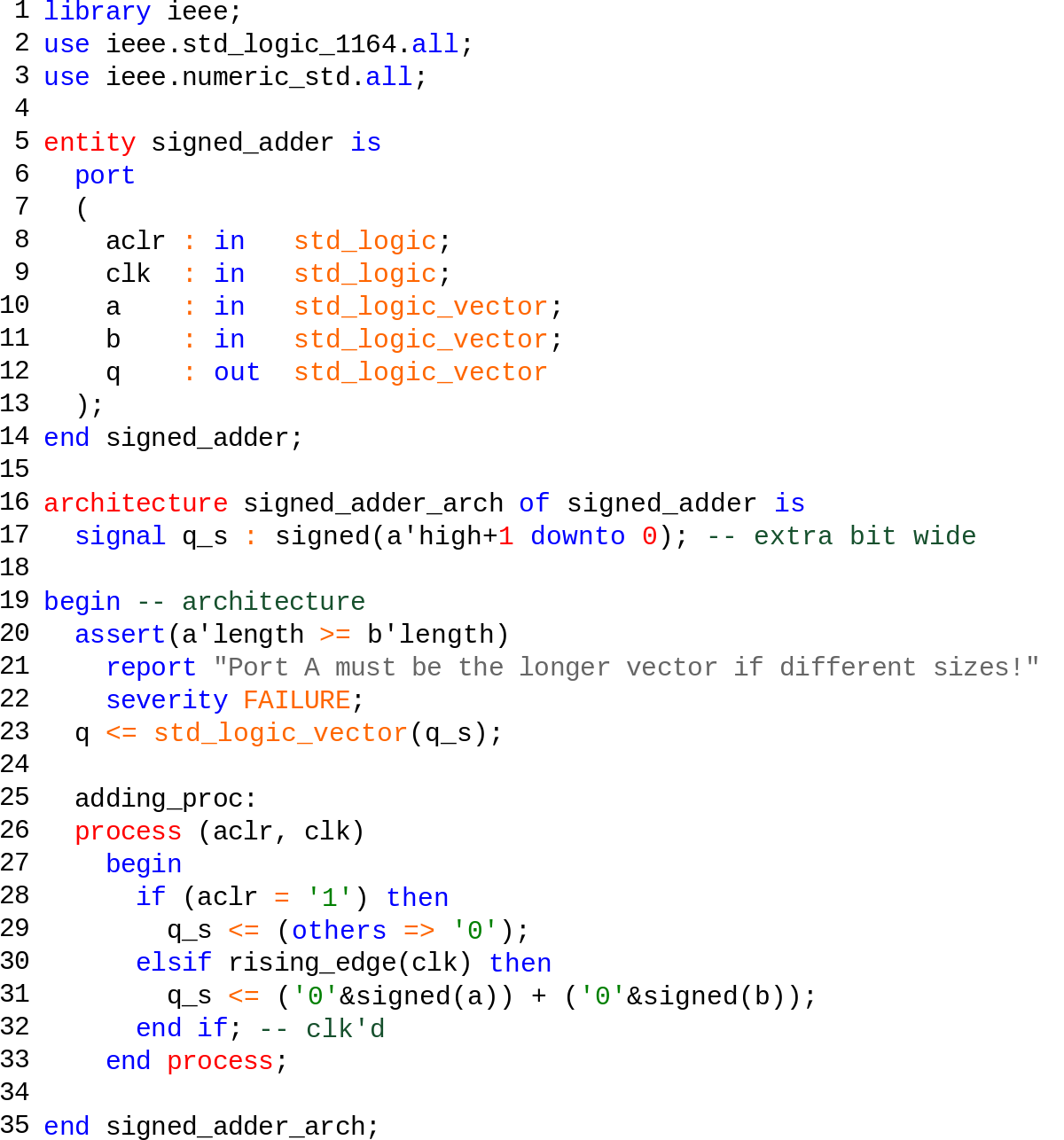

28VHDL program for implementing a 81 multiplexer using if-else statements. 4 If-statements and case statements must be completely specified or VHDL compiler infers latches.

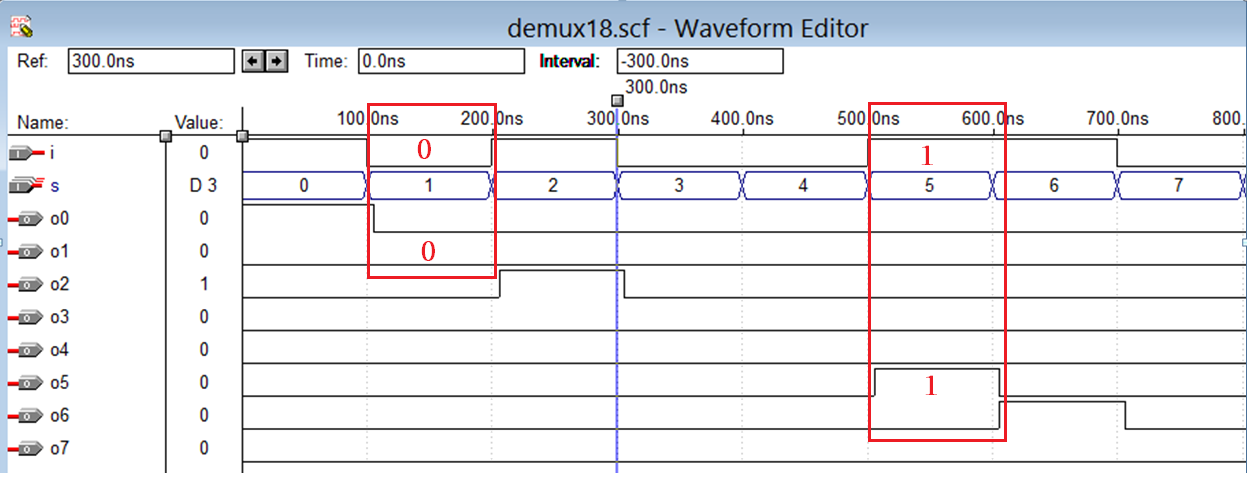

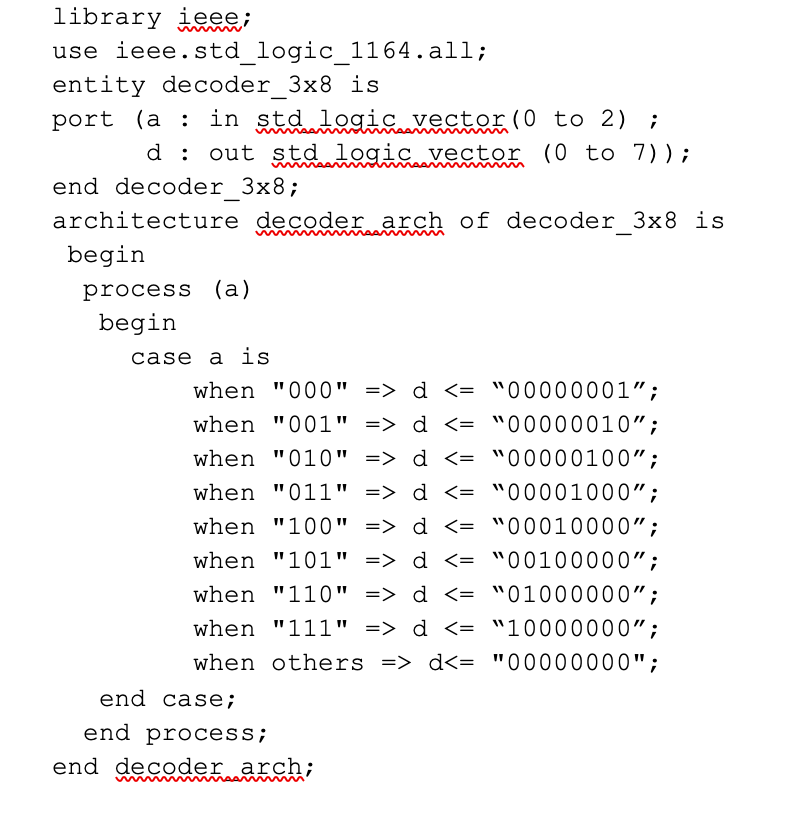

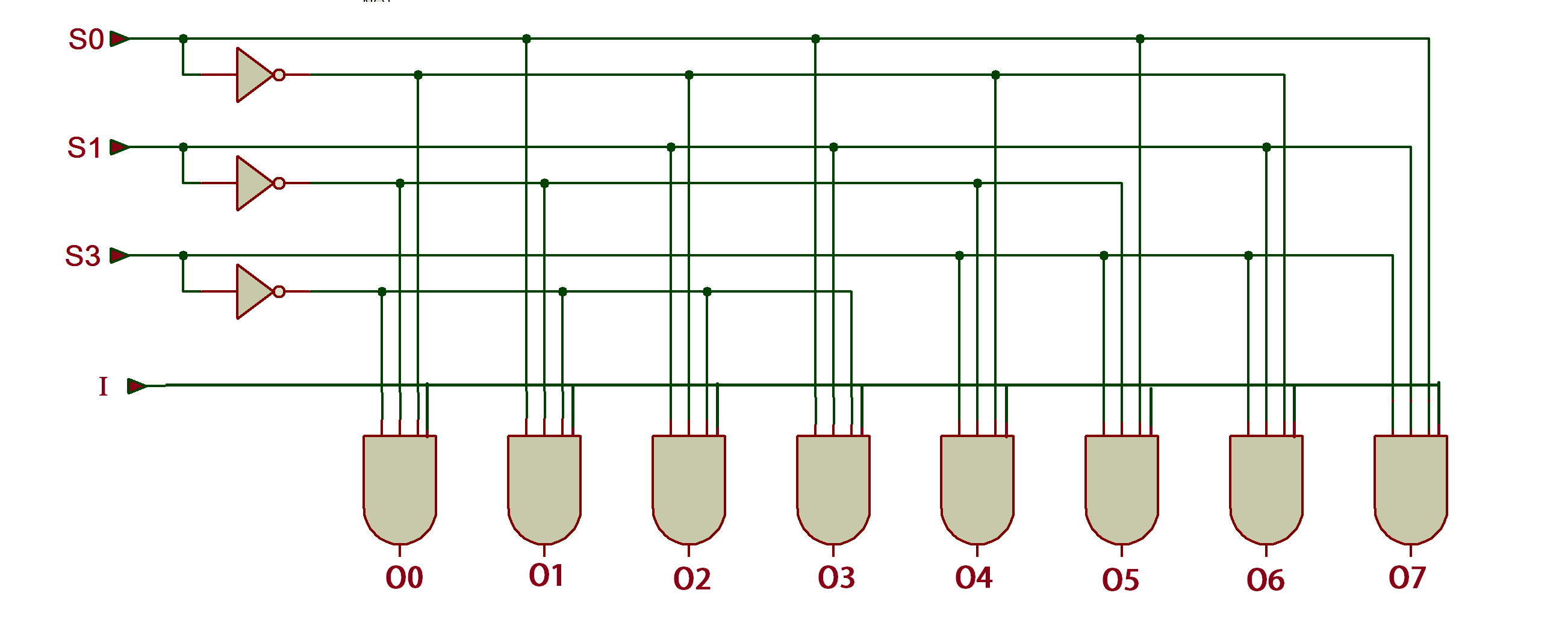

Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl

| Title: Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: PDF |

| Number of Views: 3020+ times |

| Number of Pages: 142+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: October 2018 |

| Document Size: 2.1mb |

| Read Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

|

A default assignment must be made so that an assignment occurs for all conditions.

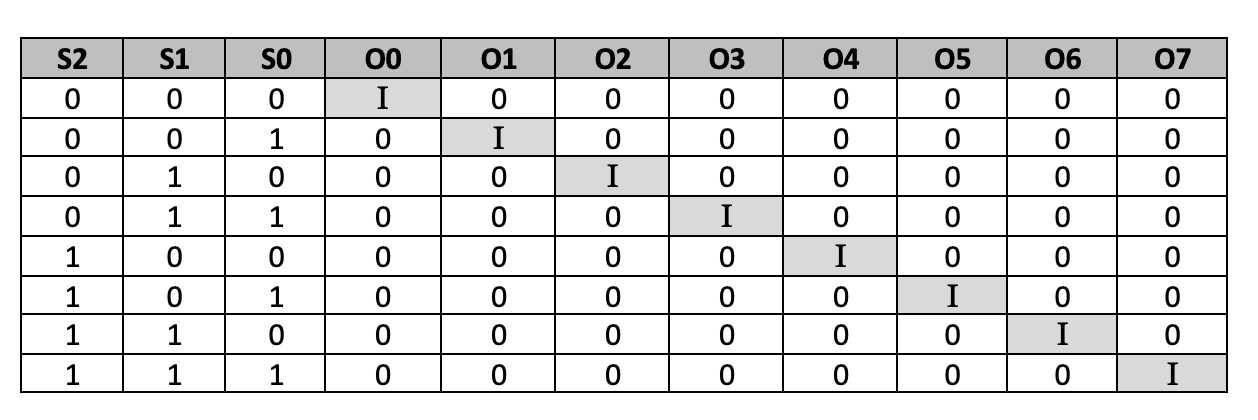

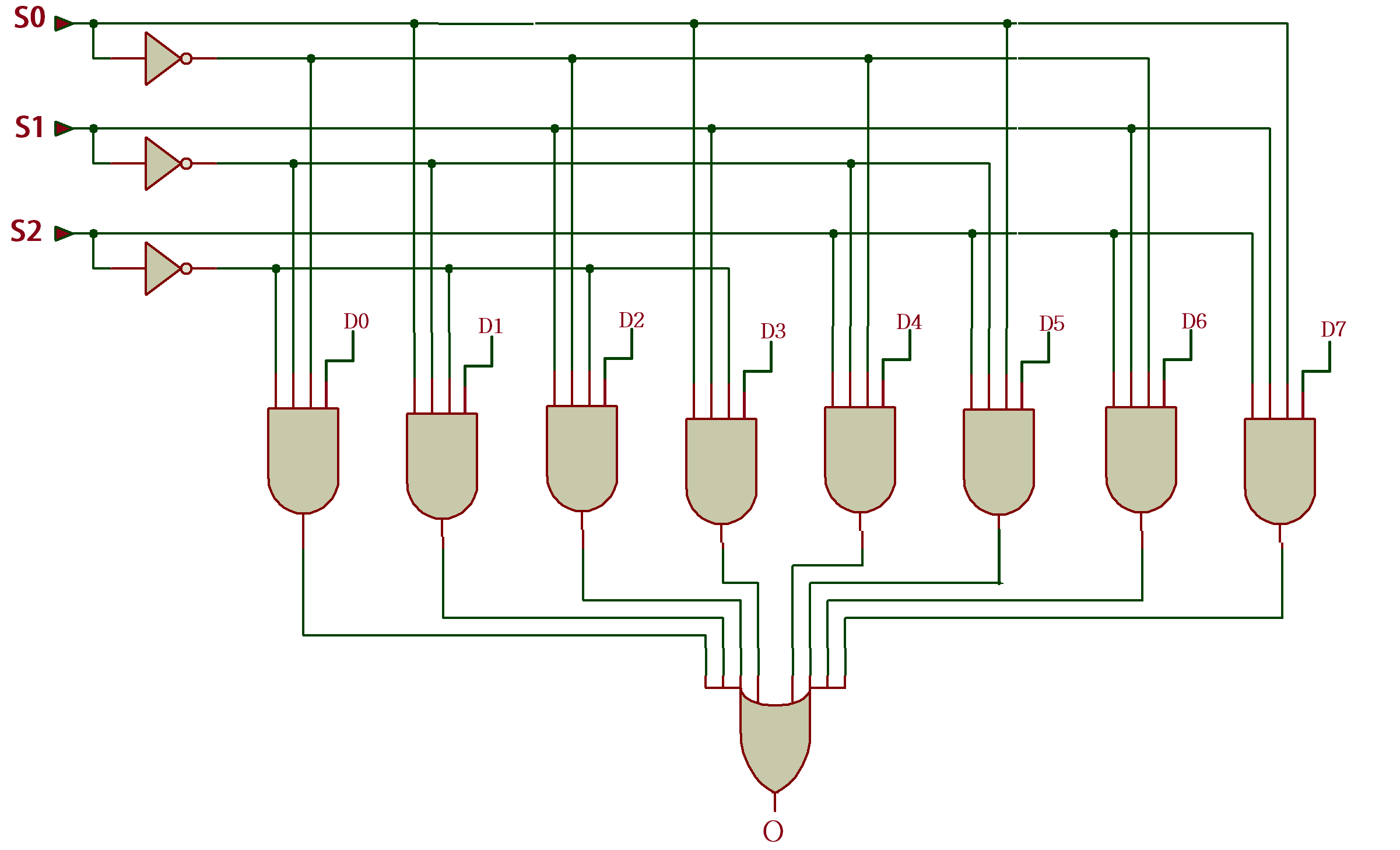

As shown in the figure one can see that for select lines S2 S1 S0 011 and 100 the inputs d31 and d41 are available in output o1. 4 to 1 Multiplexer VHDL. When writing testbench like I did or using that package in any other VHDL design following line is necessary. A quick note on using package. 17Demultiplexer with vhdl code 1. This page of verilog sourcecode covers HDL code for 8 to 1 Multiplexer using.

Lesson 20 Vhdl Example 8 4 To 1 Mux Case Statement

| Title: Lesson 20 Vhdl Example 8 4 To 1 Mux Case Statement Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Doc |

| Number of Views: 3220+ times |

| Number of Pages: 202+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: December 2017 |

| Document Size: 1.8mb |

| Read Lesson 20 Vhdl Example 8 4 To 1 Mux Case Statement |

|

Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl

| Title: Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Doc |

| Number of Views: 3240+ times |

| Number of Pages: 302+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: August 2020 |

| Document Size: 1.5mb |

| Read Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

|

Tutorial 20 Verilog Code Of 8 To 1 Mux Using 2 To 1 Mux Concept Of Instantiation Vlsi

| Title: Tutorial 20 Verilog Code Of 8 To 1 Mux Using 2 To 1 Mux Concept Of Instantiation Vlsi Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Doc |

| Number of Views: 8141+ times |

| Number of Pages: 83+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: January 2021 |

| Document Size: 1.1mb |

| Read Tutorial 20 Verilog Code Of 8 To 1 Mux Using 2 To 1 Mux Concept Of Instantiation Vlsi |

|

Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl

| Title: Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: PDF |

| Number of Views: 8194+ times |

| Number of Pages: 276+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: August 2021 |

| Document Size: 800kb |

| Read Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

|

Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl

| Title: Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Google Sheet |

| Number of Views: 7181+ times |

| Number of Pages: 268+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: February 2017 |

| Document Size: 2.1mb |

| Read Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

|

8 To 1 Multiplexer Vhdl Code

| Title: 8 To 1 Multiplexer Vhdl Code Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Doc |

| Number of Views: 5158+ times |

| Number of Pages: 259+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: August 2017 |

| Document Size: 3mb |

| Read 8 To 1 Multiplexer Vhdl Code |

|

8 Bit Puter In An Fpga 8 Bit Puter Bits

| Title: 8 Bit Puter In An Fpga 8 Bit Puter Bits Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Doc |

| Number of Views: 8186+ times |

| Number of Pages: 7+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: May 2017 |

| Document Size: 3.4mb |

| Read 8 Bit Puter In An Fpga 8 Bit Puter Bits |

|

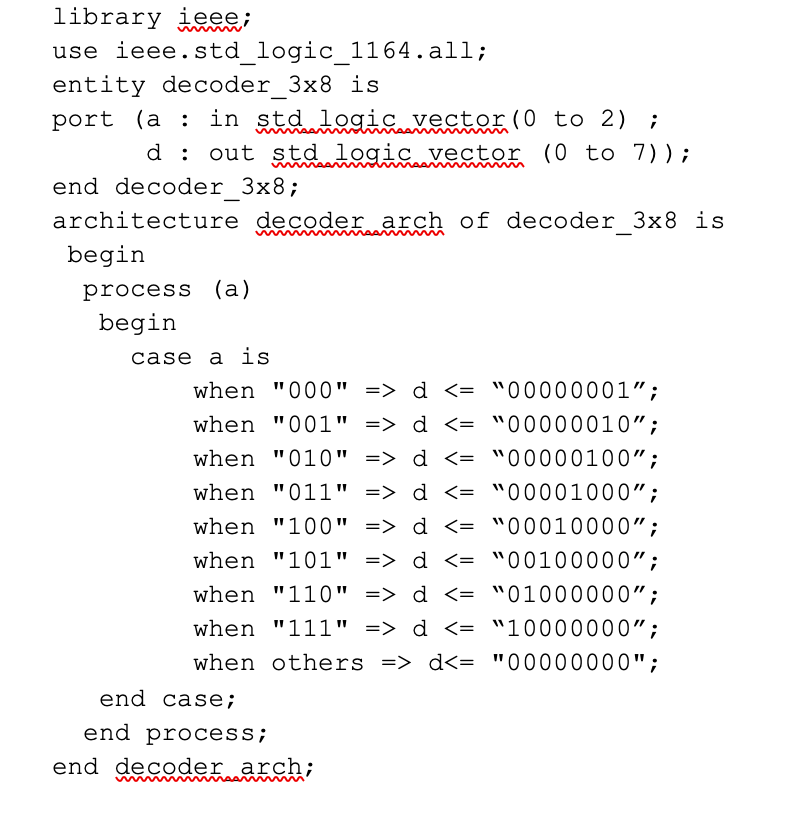

Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl

| Title: Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: PDF |

| Number of Views: 8203+ times |

| Number of Pages: 168+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: May 2020 |

| Document Size: 2.3mb |

| Read Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl |

|

Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl

| Title: Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Doc |

| Number of Views: 8135+ times |

| Number of Pages: 164+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: February 2020 |

| Document Size: 1.6mb |

| Read Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

|

Zgtxueegro9xnm

| Title: Zgtxueegro9xnm Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Doc |

| Number of Views: 4172+ times |

| Number of Pages: 321+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: October 2017 |

| Document Size: 1.8mb |

| Read Zgtxueegro9xnm |

|

8 To 1 Multiplexer Vhdl Newdisplay

| Title: 8 To 1 Multiplexer Vhdl Newdisplay Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Format: Google Sheet |

| Number of Views: 8168+ times |

| Number of Pages: 158+ pages about Vhdl Code For 8 To 1 Multiplexer Using If Statement |

| Publication Date: March 2020 |

| Document Size: 725kb |

| Read 8 To 1 Multiplexer Vhdl Newdisplay |

|

A quick note on using package. 15VHDL Code----- Title. This page of verilog sourcecode covers HDL code for 8 to 1 Multiplexer using.

Here is all you need to know about vhdl code for 8 to 1 multiplexer using if statement 20Next let us move on to build an 81 multiplexer circuit. This page of verilog sourcecode covers HDL code for 8 to 1 Multiplexer using. Using Concurrent Signal Assignment Statement Here is the general format of a concurrent signal assignment statement. Vhdl tutorial 14 design 1 8 demultiplexer and 8 1 multiplexer using vhdl vhdl tutorial 14 design 1 8 demultiplexer and 8 1 multiplexer using vhdl tutorial 20 verilog code of 8 to 1 mux using 2 to 1 mux concept of instantiation vlsi vhdl tutorial 14 design 1 8 demultiplexer and 8 1 multiplexer using vhdl vhdl tutorial 14 design 1 8 demultiplexer and 8 1 multiplexer using vhdl 8 to 1 multiplexer vhdl code zgtxueegro9xnm vhdl tutorial 13 design 3 8 decoder and 8 3 encoder using vhdl Verilog code for 81 mux using gate-level modeling.